# FPGA Implementation of Doppler Processing for Human Heart-beat Detection and Ranging Through a Barrier using UWB SFCW approach

Nemani Sirisha, A.D. Sandhya Rani, Paramita Barua, D. Anuradha, R.Kuloor Electronics and Radar Development Establishment DRDO Bangalore, 'A' Radar, LRDE, C.V. Raman Nagar, Bangalore, India <u>p\_barua@rediffmail.com</u>, <u>sirishanmn@gmail.com</u>

#### Abstract:

The growing security concerns worldwide have led to the development of wideband radar systems for detection of heart-beat and breathing rate of living objects especially human beings has many applications in military and bio-medical areas. Radar for detecting heart beat of an individual could also be used in many critical services such as medicine, rescue services, law and anti terrorist's enforcements. Majority of these applications focus on the use of very short pulses, (Ultra-Wideband impulse radars) which in-turn require expensive hardware and have limited range. For an accurate detection of heart beat ,a huge amount of measurements are required. This paper focuses on the FPGA implementation of a human heart-beat detection by using FFT IP cores and DDR2 SDRAM for image data storage and retrieval of multiple frames for Doppler processing. Finally the range and Doppler of a human body is plotted in Matlab by transferring the data through Chipscope Analyzer of Xilinx ISE 13.2 tool. This raw data is generated using a UWB Stepped Frequency Continuous Wave (SFCW) using Vector Network Analyser. Experimented results and frequency spectrums for heart beat, respiration and articulation of a man are presented.

### **I.INTRODUCTION**

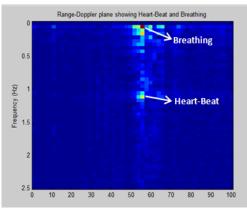

Electromagnetic waves have the ability to penetrate man-made building materials and to detect the heart beat behind the opaque structures. The frequency of human breathing can range anywhere from 0.1 to 0.5 Hz and that of heart-beat can range from 0.8 to 2.5 Hz. Hence an average value of 0.3 Hz for breathing rate and 1.5 Hz for heartbeat has been considered. The human being is assumed to be stationary. Hence, a signal with three frequencies can be expected from the human being: zeroth frequency corresponding to the stationary part of the human body and two Doppler frequencies caused by breathing and heart beat. Hence a total of 30dB (approx.) attenuation can be assumed in the reflected signal.

Fig.1: Through The Wall Human Heart-beat Detection and Ranging Model

## II. STEPPED FREQUENCY CONTINUOUS WAVE RADAR

Stepped frequency continuous wave (SFCW) radars have gained momentum since the availability of fast frequency sweeping devices. The shift in position due to a minute Doppler (such as heart beat) changes the phase of the transmitted SFCW signal. Hence, the received voltage at the receiver is a function of phase. Basically, in SFCW transmission a series of single tone frequencies are transmitted in a given frequency range. Each step corresponds to a single frequency. The frequency step size (number of data points) determines the unambiguous range. The stepped-frequency scheme approximates a wideband signal using a finite number K of monochromatic signals with equally spaced frequencies  $f_k$  covering the desired bandwidth  $f_0$  to  $f_{k-1}$ .

$$f_k = f_0 + k(\Delta f)$$

$$\Delta f = \frac{f_{k-1} - f_0}{K - 1}$$

for  $k = 0, 1, 2...K - 1$

Where  $\Delta f$  represents frequency step size.

## **III. FPGA IMPLEMENTATION**

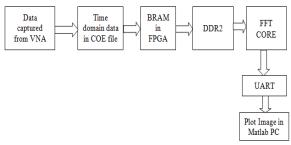

The data is collected in frequency domain through Vector Network Analyser Agilent PNA 8362B. The acquired data was converted to complex form (a+ib).The data is collected in frequency domain for 256 sweeps where each sweep consists of 256 frequency steps covering the entire bandwidth. Hence the size of the data array size is 256x256. This frequency domain data is converted to time domain data and stored in a COE file .This file is temporarily read to BRAM and stored in DDR2. Once the entire data is read in DDR2, flag can be set and data is read corresponding to each range bin for all 256 sweeps and are read in BRAM. Now FFT core reads these values and perform 256 point FFT. This is sent to Chipscope for plotting the data in Matlab in PC. This process is repeated for all range bins.

Fig. 2: Data flow Diagram of Doppler Processing Algorithm

## **IV. FAST FOURIER TRANSFORM**

The FFT core accepts complex data samples and through pipeline streaming, it pipelines several Radix-2 butterfly operations to offer continuous data processing. The input and output data format is in 16 bit fixed point format, 256 point FFT. The clock frequency is 32MHz.

The range-doppler data is transferred to PC to plot the image in Matlab using UART interface.

#### V. IMPLEMENTATION

The heart beat detection using FFT is implemented using Virtex 5 XC5FXT-2FF1738 FPGA. The IP cores and VHDL code are implemented using Xilinx 13.2 ISE tool.

| No. of transmitters    | 1     |

|------------------------|-------|

| No. of Receivers       | 1     |

| No .of Frequency steps | 256   |

| Clock Frequency        | 32MHz |

Table II Device Utilization Summary: Implementation of Doppler processing.

| Slice Logic Utilization           | Used | Available | Utilization |

|-----------------------------------|------|-----------|-------------|

| Number of Slice Register          | 9643 | 64000     | 15%         |

| Number of Slice LUT's             | 8124 | 64000     | 12%         |

| Number of occupies Slices         | 4532 | 16000     | 28%         |

| Number of fully used LUT-FF Pairs | 5346 | 12421     | 43%         |

| Number of bonded IOBs             | 117  | 680       | 17%         |

| Number of BlockRAM/FIFO           | 91   | 228       | 39%         |

| Number of BUFG/BUFGCTRLs          | 6    | 32        | 18%         |

| Number of DSP48Es                 | 12   | 256       | 4%          |

| Number of PLL_ADVs                | 1    | 6         | 16%         |

#### VI. EXPERIMENTAL SETUP AND RESULTS

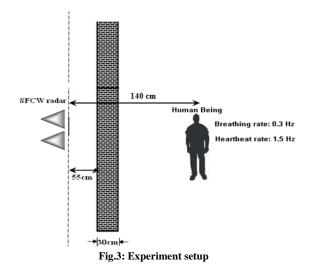

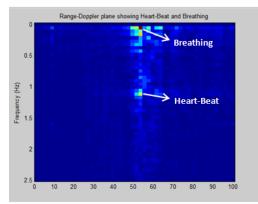

For the experimental setup, a human at a position of (0.55m, 0.0m) behind the barrier is considered as the target. The barrier is located at (0.0m, 0.0m).A UWB Stepped Frequency Continuous Wave (SFCW) of bandwidth 3GHz is generated using Vector Network Analyzer. 256 point FFT was taken along the same range bins through 256 sweeps. All the values of the first row of Range Doppler plot, which corresponds, to zero<sup>th</sup> filter have been forced to zero in order to suppress the stationary Doppler (which is high in intensity) and enhance the other Doppler frequencies. The barrier is located at 0.0m range.

Single Target Situation: A human at a position of 0.55m from the other side of the wall.

2

Fig. 4. Matlab Result

Fig. 5. FPGA Result

## **VII. CONCLUSION**

In this paper, we conclude that the FPGA implementation of Doppler processing using stepped frequency continuous wave radar signal can generate accurate detection of heart beat.

#### **VIII. REFERENCES**

- C. Lei and S. Ouyang, "Through-wall Surveillance using Ultra-wideband Short Pulse Radar: Numerical Simulation," Industrial Electronics and Applications, 2007, pp. 15511554, May 2007.

- [2]. M. Aftanas, "Signal Processing Steps for Objects Imaging Through the Wall with UWB Radar," 9th Scientific Conference of Young Researchers, SCYR 2009. Faculty of Electrical Engineering and Informatics, Technical University of Kosice, pp.14-17, May 2009.

- [3]. Immoreev and Fedotov, "Ultra wideband radar systems: advantages and disadvantages," Ultra Wideband Systems and Technologies, pp. 201205, 2002.

- [4]. Through wall sensing of Human Breathing and Heart Beating by Monochromatic Radar by A.S.Bugaev, v.vchapursky, S.S Ivashov, V.V.Razevig, A.P.Sheyko, I.A.Vasilyev

- [5]. D.J. Daniels, Surface-penetrating radar, Piscataway, NJ:IEEE Press, 1996.

## **BIO DATA OF AUTHORS**

**Nemani Sirisha** received B.Tech. degree in Instrumentation Technology from Andhra University in 2006. She is currently working as scientist in Electronics and Radar Development Establishment (LRDE). Her areas of work include embedded systems.

**A.D. Sandhya Rani** received Diploma in Computer Science Engineering from Q.Q.Govt. Polytechnic, Hyderabad in 2005 and pursuing B.Tech. in Computer Engineering from JNTU, Hyderabad.

She is currently working as Senior Technical Assistant in Electronics and Radar Development Establishment (LRDE). Her areas of work include Radar Signal Processing.

**Paramita Barua** received B.E. in Electronics and Telecommunication Engineering from Rajiv Gandhi Prodyogiki Vishwavidyalaya, Bhopal in 2001. She is currently working as

Scientist in Electronics and Radar Development Establishment (LRDE). Her areas of work include Radar Signal Processing.

**D.** Anuradha obtained her B.Tech. in Electronics and Communication Engineering from J.N.T.U Hyderabad in 1987. She has worked in DRDL in the IGMDP Programme upto 2005.

She is presently heading the Radar Signal Processing Group of A Radar in LRDE

**Ramachandra Kuloor** obtained his BE from UVCE, Bangalore in 1976 & ME from Dept. of ECE, IISC, Bangalore in 1978. He joined LRDE in 1978 and has been working in the area of radar signal processing. His

areas of interest include radar ECM techniques and FPGA based low power signal processor realization. He is a recipient of the IETE-IRSI award 1996-1997 and AGNI award for self-reliance in 2002.